## Reduction of leakage current of poly-Si TFTs with metal source/drain by dual gate structure

Taisei Harada<sup>1</sup>, Takuya Ashitomi<sup>1</sup>, Kiyoharu Shimoda<sup>1</sup>, Wataru Narisoko<sup>1</sup>, Tatsuya Okada<sup>1</sup> and Takashi Noguchi<sup>1</sup>, Osamu Nishikata<sup>2</sup>, Atsushi Ota<sup>2</sup> and Kazuya Saito<sup>2</sup> Sang-Yun Kim<sup>3</sup>, Jin-Kuk Kim<sup>3</sup> and Byung Seong Bae<sup>3</sup> <sup>1</sup>Faculty of Engineering, University of the Ryukyus, 1 Senbaru, Nishihara, Okinawa 903-0213, Japan <sup>2</sup>ULVAC, Inc., Kanagawa, Japan <sup>3</sup>Hoseo University, Chungnam, Korea

Tel.:+81-98-895-8680, E-mail: k158531@eve.u-ryukyu.ac.jp

LTPS (Low Temperature Poly-Silicon) TFTs (Thin Film Transistors) with high mobility have a number of advantages for O-LED (Organic-Light Emitting Diode) pixel and for LCD (Liquid Crystal Display) such as low power consumption and integrating functional circuits on a panel. Recently, BLDA (Blue Laser Diode Annealing) was reported as a next generation LTPS process. BLDA can heat up the thin Si film uniformly by slightly deeper penetration depth than UV laser and is expected to obtain uniform grain size with reduced surface roughness [1]. Also, our group has proposed and shown simple TFT structure with metal source/drain without using impurity doping [2]. Although Si TFT with metal source/drain of Ti is expected to reduce the fabrication cost [2], leakage current seems to be rather higher than conventional doped source/drain. Dual-gate TFT structure of series connection is expected to be effective for reducing the off leak current [3].

Top gate structured poly Si TFTs using BLDA have been fabricated on glass substrates. For the TFT fabrication, channel Si layer of 50 nm thickness was deposited by PE CVD and subsequently dehydrogenated at 490°C. The beam size was controlled at  $600 \times 2.4 \ \mu\text{m}^2$  and the Si films were crystallized by BLDA at 5 W. After patterning the Si film for TFT channel, subsequent hydrogenation at 400°C for 60 min. Ti as a metal source/drain was deposited using vacuum evaporation. After patterning the Ti film, SiO<sub>2</sub> film of 100 nm thickness was deposited as a gate insulator at room temperature using RF sputtering. After patterning the SiO<sub>2</sub> for contact holes, Al electrodes were evaporated. Finally, the TFT was annealed at 400°C for 60 min in H<sub>2</sub>/N<sub>2</sub> (4%) atmosphere to reduce the defects in Si and Si/SiO<sub>2</sub> interface. Besides of TFT fabrication, device simulation for the conventional structured poly-Si TFT has been conducted as a comparison.

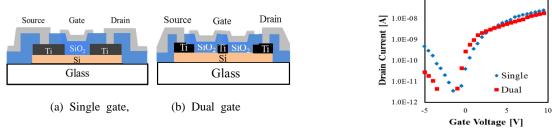

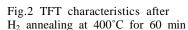

Fig.1 shows cross-sectional view of single gate and dual gate TFT. Fig.2 shows transfer curves of poly Si TFT (L/W = 20  $\mu$ m/5  $\mu$ m, V<sub>d</sub> = 1 V) after H<sub>2</sub> annealing for 60 min. Considerable reduction of off leak current for dual gate structure is observed. In conventional n<sup>+</sup> source/drain structure, the effect of the leakage reduction was also observed by simulation.

By applying the dual gate structure for the LTPS TFT with metal source/drain structure, reduction of leakage current which affects to stable driving with saving power is expected.

Fig.1 Cross-sectional view of TFT

1.0E-07

## References

- 1. T. Noguchi, Y. Chen, T. Miyahira, J. D. Mugiraneza, Y. Ogino, Y. Iida, E. Sahota, and M. Terao, Jpn. J. of Appl. Phys., 49, 03CA10-1-3 (2010).

- 2. K. Shimoda, K. Sugihara, T. Okada and T. Noguchi, Proc. of iMiD'13, p.200, (2013)

- 3. Y.-C. Wu, T.-C. Chang, P.-T. Liu, C.-W. Chou, Y.-C. Wu, C.-H. Tu, and, C.-Y. Chang, IEEE Ele. Dev. Lett., vol.26, p.646, (2005).