## A Novel Pull-Down Structure for High-Performance ASG Driver Circuits

Yiming Li<sup>\*</sup>, Chien-Hsueh Chiang

## Parallel and Scientific Computing Laboratory, Institute of Communication Engineering, Department of

Electrical and Computer Engineering, National Chiao Tung University, Hsinchu 300, Taiwan

\*Corresponding Author. Phone: +886-3-5712121 ext. 52974 Fax: +886-3-5726639 E-mail: ymli@faculty.nctu.edu.tw

For nowadays advanced liquid crystal display (LCD) applications, the amorphous silicon gate driver (ASG) circuits embedded in a display panel become main stream [1-4]. Proper fall time of the gate output makes the pixel TFTs to be charged with correct data voltage in time. However, a long fall time may cause incorrect data voltage to the pixel TFT. In this work, we report a novel ASG circuit. In this structure, the measured fall time of the designed and implemented circuit is 17% shorter than that of the original one. Notably, the total layout area of the explored ASG driver circuit is almost invariable relatively.

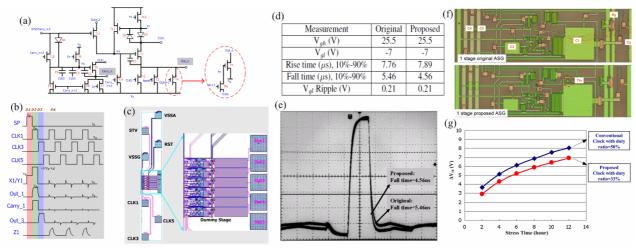

As shown in Fig. 1(a), as a symbolic representation, the single stage ASG circuit is composed of seventeen TFTs and four capacitances with three external clock signals. By importing the internal signals to enhance the discharging capability of the pull-down TFT, the fall time could be reduced effectively. The relative timing chart is shown in Fig. 1(b). In order to retard the  $V_{th}$  shift effect, the 3-phases clocks were applied in the circuit. The 6-stages circuit whose layout is shown in Fig. 1(c) was fabricated using a 5-mask process. Each output was connected to a resistance (1.35 K $\Omega$ ) and a capacitance (75.5 pF) as loading. The measurement data of the circuits are listed in Fig. 1(d). As we can see that their performances are almost identical except the important characteristic, the fall time, is 17% shorter than that of the original one. The realistic output waveforms between the original and proposed circuits are observed from Fig. 1(e). Besides, the layout areas are identical in both circuits as shown in Fig. 1(f). In order to verify the 3-phases clock that can alleviate the V<sub>th</sub> shift, measuring the V<sub>th</sub> shift values every two hours for the clocks with different duty ratios as shown in Fig 1(g). After 12-hours high-temperature (60°C) stressing, the magnitude of V<sub>th</sub> shift under the clock with 33% duty ratio was about 6.9 V that was smaller about 15% than that (8.1V) of the clock with 50% duty ratio.

Fig. 1. (a) The applied ASG circuit. (b) The timing chart of the proposed 3-phase clocks (c) The layout of the 6-stages ASG circuit with integrated RC loading. (d) The measurement data of the implemented samples. (e) The fall time of the original circuit was 5.46  $\mu$ s and the proposed one was 4.56  $\mu$ s in the measured waveforms. (f) The optical photo of the original and proposed ASG circuits. (g) The V<sub>th</sub> shift measurement of two clocks biasing with different duty ratio for an a-Si:H TFT under the temperature (60°C) in 12 hours.

## References

- 1. C.-H. Chiang et al., IMID'13 Technical Digest, p. 176 (2013).

- 2. H.-W. Cheng et al., IMID'09 Technical Digest, p. 968 (2009).

- 3. P.-J. Lin et al., IMID'11 Technical Digest, p. 78 (2011).

- 4. Y.-Y. Chen et al., IMID'12 Technical Digest, p. 268 (2012).