## New shift register circuit scheme for stable output using oxide TFTs

## Jae-Eun Pi, Sung Haeng Cho, Chun-Won Byun, Jong-Heon Yang, Ji-Hun Choi, Oh Sang Kwon, Eun Suk Park, Chi-Sun Hwang

Smart I/O Control Device Research Section, ETRI, Daejeon 305-700, Korea

*Tel.:82-42-860-1715, E-mail: jepi@etri.re.kr*

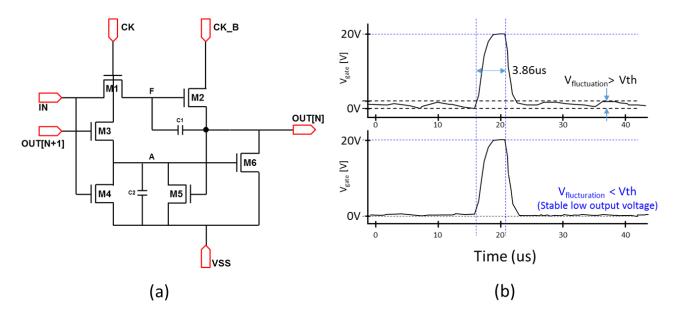

A new shift register circuit using oxide thin-film transistor (TFT) is proposed. As ever, it is important to research for promising high resolution and large size active matrix panel in display industry. For stable gate line operation expecially low voltage output, dual pull-down scheme using AC bias alternately has been widely used by many researchers to overcome degradation causing DC bias stress. However, recent display device for example oxide TFT has been impressively developed and is almost done to solve degradation problem in DC bias stress. First of all, we fabricated Back channel etch structure TFT device for display backplane, and we extracted parameters for spice simulation. As our research, dual pull-down circuit scheme give rise to circuit complexity and is not suitable to realize low power consumption owing to added clock and DC signal line. So we propose new shift register circuit with single pull-down circuit scheme using oxide TFT. Fig 1. (a) shows a schematic of a proposed shift register circuit composed of 6 TFTs and 2 capacitors. Continously single pull-down block is designed to protect output node from clock coupling when low output operation. And it is designed for successful operation in high frequency 130kHz for UHD display.

Fig. 1. (a) The schematic of new shift register circuit, (b) concept results for stable low output voltage

## Acknowledgment

This research has been supported by the Giga Korea Development of Telecommunications Terminal with Digital Holographic Table-top Display [GK13D0100].

## References

- 1. Seung-Jin Yoo, Sung-Jin Hong, Jin-Seong Kang and Oh-Kyong Kwon, IEEE Electron Device Letters, VOL. 33, NO. 3, March 2012

- 2. Kazushige Takechi, Mitsuru Nakata, Kazufumi Azuma, Hirotaka Yamaguchi, and Setsuo Kaneko, IEEE Transaction On Electron Devices, VOL. 56, NO. 9, SEP 2009

- 3. C-S Hwang, S-H Ko Park, IMID `11 Technical Digest, P. 64 (2011)

4. J. E. Pi IMID `10 Technical Digest, P. 118 (2010)