## Volume Transport in Dual-Gate Thin-Film Transistors Using Ultra-Thin Amorphous Oxide and Polymer Semiconductors

## Yong Xu and Yong-Young Noh

Dept. of Energy and Materials Engineering, Dongguk Univ., 26 Pil-dong, 3 ga Jung-gu, Seoul 100-715, Korea

Tel.:+82-2-2260-4974, E-mail: <u>xu.yong@dongguk.edu</u>, <u>yynoh@dongguk.edu</u>

The display industry is fast evolving for the ceaseless demand for large area, flexible, low power consu mption, high resolution, and low cost applications, which has stimulated the introduction of new switchin g devices to replace the present silicon-based technologies. Metal oxide and organic thin-film transistors (TFTs) are believed to be promising in this respect. These new devices, however, may still suffer from 1 ow performance and poor stability as well as large parameter variations particularly for those manufactur ed by solution-based processing. In this work, we present that dual-gate (DG) TFTs can offer a great op portunity to overcome such issues and thus enable their practical use in future displays.

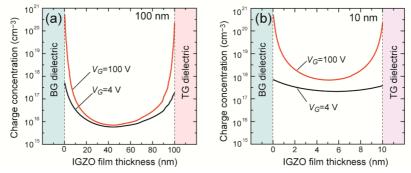

Fig. 1 shows the simulation results of two DG IGZO TFTs having different semiconductor thicknesses. One can readily recognize the difference: electron accumulation is only at the two surfaces for 100 nm-t hick IGZO yet as the thickness is reduced to 10 nm the charge transport extends into the entire film thi ckness due to electrical field coupling of the two gates inducing volume charge transport in semiconduct or bulk. Compared to surface counterpart, volume transport is less susceptible to the detrimental influenc es arising from the contacting gate dielectrics and their interfaces, i.e., being more intrinsic with superior

carrier mobility, stability, and uniformity. Meanwhile, full depletion can lead to very low off current th at is instrumental to reducing power consumption and improvement of dynamic spanning. By incorporatio n of ultra-thin films of amorphous oxide and polymer semiconductors, we show that efficient volume tra nsport can be achieved in dual-gate TFTs and the underlying mechanisms are also revealed.

Fig. 1. Simulated charge distribution profile in two dual-gate transistors with IGZO film thickness of 100 nm (a) and 10 nm (b), where BG and TG dielectrics represent the bottom-gate dielectric (300 nm SiO<sub>2</sub>) and the top-gate dielectric (500 nm PMMA), respectively.

## Acknowledgment

This work was supported by the Center for Advanced Soft-Electronics (2013M3A6A5073183) funded by the Ministry of Science, ICT & Future Planning and LG electronics Research Fund.